# Point-of-Load Pulse Emulator for High-Performance Testing

Diego A. Puerta, Electrical Engineering Mentor: Mike K. Ranjram, Assistant Professor School of Electrical, Computer and Energy Engineering

## **Research Question**

How can we emulate the load of a 4kW pulsed power converter for accurate testing?

#### Methods

Explored switched-resistor and switched-inductor solutions.

Computed maximum allowable parasitics to achieve desired performance under worst-case conditions (slew 222A in 5ns).

Ran LTspice simulations to analyze dynamic responses with real switch implementations.

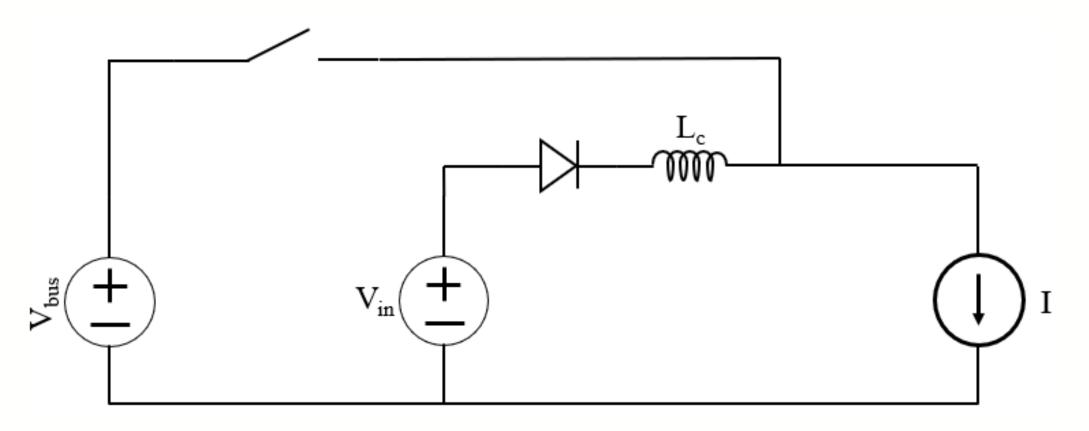

Fig. 1: model for an inductive-input converter switched to emulate a pulse at the bus with a commutating inductance.

#### Results

We can compute the maximum allowable commutating inductance for the topology in Fig. 1 to be:

$$L_{c-max} = \frac{V_{bus} - V_{in}}{I} t_{rise}$$

[H]

Under worst-case conditions:

$$L_{c-max} = 67.5 \text{pH}$$

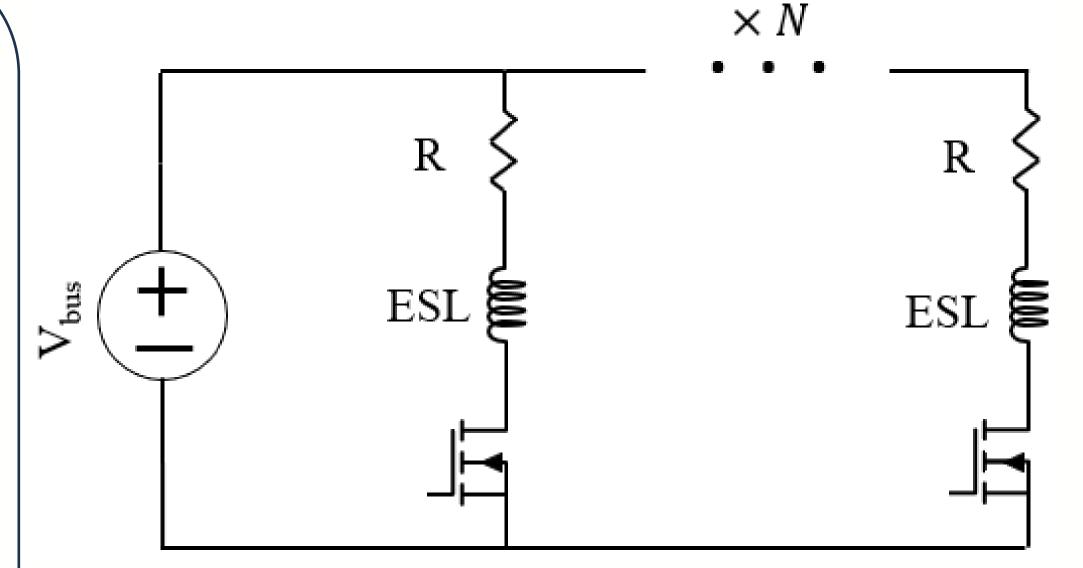

LTspice simulations of the switched-resistor network in Fig. 2 showed ability to match desired slew rates with ideal switches.

LTspice simulations of the switched-resistor array with a  $10\Omega$  Ohmite TKH45 resistor (ESL of 14.5nH) and a EPC2035 GaNFET show ringing on the turn-off portion of the pulse.

This ringing comes from the interaction of the resistor's ESL and the switch's output capacitance.

Fig. 2: switched-resistor array with parasitic ESL

#### Conclusion

The switched-inductor solution faces too many challenges in terms of parastics to be viable. The switched-resistor solution is promising, but choosing the right components and physical layout will be key to optimizing performance.

### **Future Work**

Choose components, lay out the switchedresistor array in Altium, and test a physical implementation on the bench.