# Design of Mixed-Signal Circuit Board for RRAM (Resistive Random-Access Memory) Crossbar Testing

Jaafar Al Shamari, Electrical Engineering Mentor: Dr. Ivan Sanchez Esqueda, Assistant Professor School of Electrical, Computer and Energy Engineering (ECEE)

## Motivation

With increased use of artificial intelligence and machine learning, interest has grown in custom on-chip hardware implementations to accelerate these algorithms. An integral computation within these algorithms is dot-product multiplication, which, through the use of new memristor technology, can be executed faster and with higher power efficiency than traditional CMOS circuits.

## **Problem Statement**

This project seeks to test the hypothesis that resistive randomaccess memory (RRAM) devices in a crossbar configuration can be used to implement operations such as vector-matrixmultiplication to accelerate the hardware implementation of machine learning algorithms.

# Background

### What is a memristor?

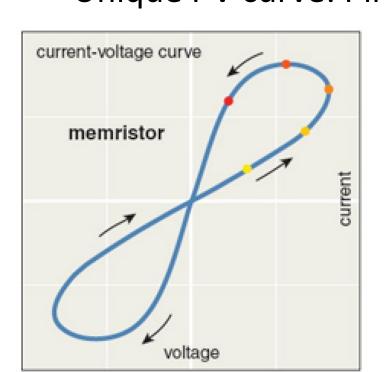

- A newly-utilized device that holds variable resistances based on input voltages.

- Unique I-V curve: Pinched Hysteresis Loop

Figure 1. Memristor I-V Curve

Figure 3. a. Memristor Crossbar Array

b. Cross-Sectional Schematic of Boron-Nitrite **Devices Used**

## Methods

### **Compound Memristive Synapse:**

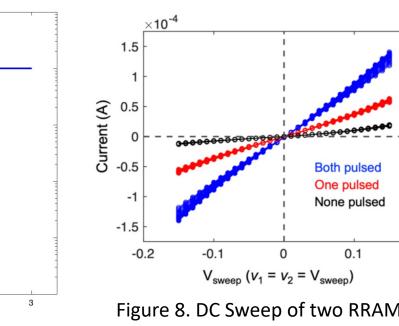

Due to volatility in the fabricated devices, the dot-product computation was not feasible to compute, and thus a simpler demonstration was produced –the compound memristive <u>synapse</u> – which employs multiple bistable memristors in parallel to form one synapse. This can be computed by:

- Pulsing positive voltages on a device in high resistance state (HRS) to set to low resistance state (LRS)

- Applying a small, non-conductance changing voltage (ranging from -.2 V to .2 V) on the top electrodes

- Grounding the bottom electrode

- Measuring total output current

- Repeat, changing each memristor state from HRS to LRS iteratively

#### Hardware methodology:

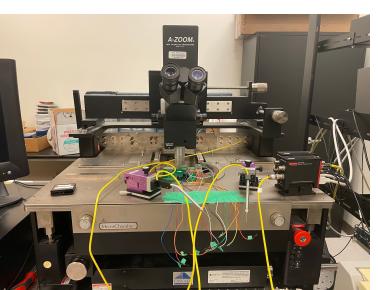

The electrical characterization was conducted on a Cascade semi-automatic probe station using a Keithley 4200 semiconductor characterization system, and on a National Instruments (NI) PXI system. The DC I-V measurements were performed using source measure units (SMUs) with the Keithley system, and an Analog Output Device (AO) with the NI. The pulse programming experiments use a combination of pulse measure units (PMUs) for programming pulses and SMUs for reading currents, switching automatically using a Keithley remote amplifier/switch (4225-RPM).

Figure 7. Measured DC Sweep of RRAM Device

from -3.5 V to +3.5 V.

Figure 5. Probe Card on Wafer

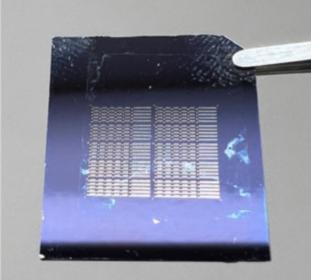

Figure 6. h-BN Memristor Array on

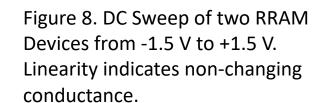

Figure 9. Average Conductance of RRAM Device After 5 Cycles. First 50 pulses: +.6 V. Second 50 pulses: -.72 V.

### Results

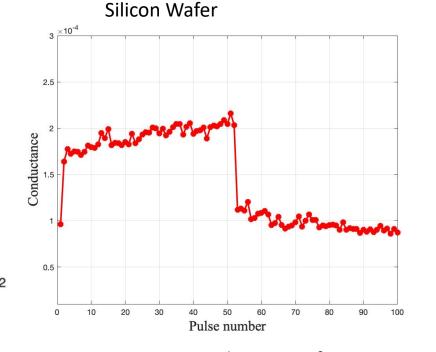

Figure 10. Current vs Memristor state of 3 RRAM devices in a row.

First state: All devices in HRS. Second state: First device in LRS, rest in HRS.

Third state: Two devices in LRS, third in HRS.

Fourth state: All devices in LRS.

The linearity of this graph highlights the ability to utilize multiple RRAM devices as one reliable synapse for use in Al implementation.

### Future Research

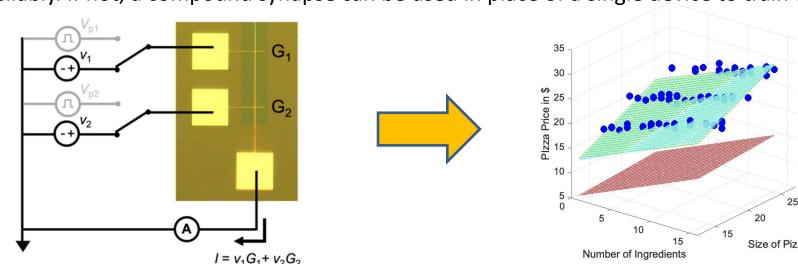

Future research can explore the hardware implementation of a linear regression model as seen by figure 11.a below if fabrication improves and devices are able to hold continuous conductances reliably. If not, a compound synapse can be used in place of a single device to train the same model.

Figure 11. a. Schematic of memristor setup for dot-product operation.

Figure 11. b. Model prediction fit to training data before training (red) and after (green)

# Conclusion

Memristors are viable devices to use in dot-product multiplication, and thus pose as unique solutions to AI/ML acceleration. However, due to the volatility of the boron-nitrite (h-BN) devices, a simpler demonstration, the compound memristive synapse, was conducted to highlight the unique characteristics and possible implementations of RRAM devices.

# Acknowledgements

Thank you to Dr. Ivan Sanchez Esqueda for developing my knowledge in this interesting field, and a special thank you to Sahra Afshari for taking the time to introduce me to the hardware and helping with testing and data collection.